Springer Berlin Heidelberg New York Hong Kong London Milan Paris Tokyo

# Embedded Software

Third International Conference, EMSOFT 2003 Philadelphia, PA, USA, October 13-15, 2003 Proceedings

Volume Editors

Rajeev Alur Insup Lee University of Pennsylvania Department of Computer and Information Science 3330 Walnut Street, Philadelphia PA 19104-6389, USA

E-mail: {alur,lee}@cis.upenn.edu

Cataloging-in-Publication Data applied for

A catalog record for this book is available from the Library of Congress.

Bibliographic information published by Die Deutsche Bibliothek Die Deutsche Bibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data is available in the Internet at <a href="http://dnb.ddb.de">http://dnb.ddb.de</a>>.

CR Subject Classification (1998): C.3, D.1-4, F.3

ISSN 0302-9743 ISBN 3-540-20223-4 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of BertelsmannSpringer Science+Business Media GmbH

http://www.springer.de

© Springer-Verlag Berlin Heidelberg 2003 Printed in Germany

Typesetting: Camera-ready by author, data conversion by PTP Berlin GmbH Printed on acid-free paper SPIN: 10960394 06/3142 5 4 3 2 1 0

## **Preface**

The purpose of the EMSOFT series is to provide an annual forum to researchers, developers, and students from academia, industry, and government to promote the exchange of state-of-the-art research, development, and technology in embedded software. The previous meetings in the EMSOFT series were held in Lake Tahoe, California in October 2001, and in Grenoble, France in October 2002. This volume contains the proceedings of the third EMSOFT held in Philadelphia from October 13 to 15, 2003. This year's EMSOFT was closely affiliated with the newly created ACM SIGBED (Special Interest Group on Embedded Systems).

Once the strict realm of assembly programmers, embedded software has become one of the most vital areas of research and development in the field of computer science and engineering in recent years. The program reflected this trend and consisted of selected papers and invited talks covering a wide range of topics in embedded software: formal methods and model-based development, middleware and fault-tolerance, modeling and analysis, programming languages and compilers, real-time scheduling, resource-aware systems, and systems on chips. We can only predict that this trend will continue, and hope that the void in universally accepted theoretical and practical solutions for building reliable embedded systems will be filled with ideas springing from this conference. The program consisted of six invited talks and 20 regular papers selected from 60 regular submissions. Each submission was evaluated by at least four reviewers.

We would like to thank the program committee members and reviewers for their excellent work in evaluating the submissions and participating in the online program committee discussions. Special thanks go to Alan Burns (University of York, UK), Alain Deutsch (Polyspace Technologies, France), Kim G. Larsen (Aalborg University, Denmark), Joseph P. Loyall (BBN Technologies, USA), Keith Moore (Hewlett-Packard Laboratories, USA), and Greg Spirakis (Intel, USA) for their participation as invited speakers. We are also grateful to the Steering Committee for helpful guidance and support.

Many other people worked hard to make EMSOFT 2003 a success, and we thank Stephen Edwards for maintaining the official Web page and handling publicity, Oleg Sokolsky and Kathy Venit for local arrangements, Usa Sammapun for setting up the registration Web page, and Li Tan for putting together the proceedings. Without their efforts, this conference would not have been possible, and we are truly grateful to them.

We would like to express our gratitude to the US National Science Foundation and the University of Pennsylvania for financial support. Their support helped us to reduce the registration fee for graduate students.

## **Organizing Committee**

Rajeev Alur (University of Pennsylvania) Program Co-chairs

Insup Lee (University of Pennsylvania)

Local Organization Oleg Sokolsky (University of Pennsylvania) **Publicity**

Stephen Edwards (Columbia University)

## **Program Committee**

Rajeev Alur, Co-chair (University of Pennsylvania, USA)

Albert Benveniste (IRISA/INRIA, France)

Giorgio C. Buttazo (University of Pavia, Italy)

Rolf Ernst (Technical University of Braunschweig, Germany)

Hans Hansson (Malardalen University, Sweden)

Kane Kim (University of California at Irvine, USA)

Hermann Kopetz (Technical University of Vienna, Austria)

Luciano Lavagno (Politecnico di Torino, Italy)

Edward A. Lee (University of California at Berkeley, USA)

Insup Lee, Co-chair (University of Pennsylvania, USA)

Sharad Malik (Princeton University, USA)

Jens Palsberg (Purdue University, USA)

Martin C. Rinard (Massachusetts Institute of Technology, USA)

Heonshik Shin (Seoul National University, Korea)

Kang Shin (University of Michigan, USA)

John Stankovic (University of Virginia, USA)

Janos Sztipanovits (Vanderbilt University, USA)

Wayne Wolf (Princeton University, USA)

Sergio Yovine (Verimag, France)

## **Steering Committee**

Gerard Berry (Estrel Technologies, France)

Thomas A. Henzinger (University of California at Berkeley, USA)

Hermann Kopetz (Technical University of Vienna, Austria)

Edward A. Lee (University of California at Berkeley, USA)

Ragunathan Rajkumar (Carnegie Mellon University, USA)

Alberto L. Sangiovanni-Vincentelli (University of California at Berkeley, USA)

Douglas C. Schmidt (Vanderbilt University, USA)

Joseph Sifakis (Verimag, France)

John Stankovic (University of Virginia, USA)

Reinhard Wilhelm (Universitat des Saarlandes, Germany)

Wayne Wolf (Princeton University, USA)

### Sponsors

School of Engineering and Applied Science, University of Pennsylvania US National Science Foundation University Research Foundation, University of Pennsylvania

#### Referees

Evans Aaron Sherif Abdelwahed Astrit Ademai Luis Almeida David Arnev Andre Arnold Ted Bapty Marius Bozga Victor Braberman Benoit Caillaud Luca Carloni Paul Caspi Elaine Cheong Namik Cho Chun-Ting Chou Thao Dang Luca de Alfaro Wilfried Elmenreich Gian Luca Ferraro Diego Garbervetsky Alain Girault Flavius Gruian Zonghua Gu Rhan Ha Wolfgang Haidinger Philipp Peti Babu Pillai

Seongsoo Hong

Haih Huang Zhining Huang Thierry Jeron Bernhard Josko Gabor Karsai Jesung Kim Moon H. Kim Raimund Kirner Sanieev Kohli Ben Lee Jaeiin Lee Xavier Leroy Xiaojun Liu Thmoas Losert Florence Maraninchi Eleftherios Matsikoudis Anca Muscholl Sandeep Neema Steve Neuendorffer Ramine Nikoukhah David Nowak Ileana Ober Iulian Ober Roman Obermaisser

Sophie Pinchinat Peter Puschner Daji Qiao Wei Qin

Subbu Rajagopalan Anders Ravn Vlad Rusu Usa Sammapun Insik Shin Oleg Sokolsky Wilfried Steiner

Li Tan

Stavros Tripakis Manish Vachharajani Marisol Garcia Valls Igor Walukievicz Hangsheng Wang Shaojie Wang Shige Wang Jian Wu Yang Zhao Haiyang Zheng Rachel Zhou Xinping Zhu

## **Table of Contents**

| In | vito  | А | Cor | tril   | hut | ions     |

|----|-------|---|-----|--------|-----|----------|

|    | v = e |   |     | 11.111 |     | 11 11 15 |

| A Probabilistic Framework for Schedulability Analysis                                                | 1   |

|------------------------------------------------------------------------------------------------------|-----|

| Resource-Efficient Scheduling for Real Time Systems                                                  | 16  |

| Emerging Trends in Adaptive Middleware and Its Application to Distributed Real-Time Embedded Systems | 20  |

| Regular Papers                                                                                       |     |

| Heterogeneous Reactive Systems Modeling and Correct-by-Construction Deployment                       | 35  |

| HOKES/POKES: Light-Weight Resource Sharing                                                           | 51  |

| Rate Monotonic vs. EDF: Judgment Day                                                                 | 67  |

| Translating Discrete-Time Simulink to Lustre                                                         | 84  |

| Minimizing Variables' Lifetime in Loop-Intensive Applications                                        | 100 |

| Resource Interfaces                                                                                  | 117 |

| Clocks as First Class Abstract Types                                                                 | 134 |

| Energy-Conscious Memory Allocation and Deallocation for Pointer-Intensive Applications               | 156 |

| Space Reductions for Model Checking Quasi-Cyclic Systems                                                                    | 173 |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

| Intelligent Editor for Writing Worst-Case-Execution-Time-Oriented Programs  Janosch Fauster, Raimund Kirner, Peter Puschner | 190 |

| Clock-Driven Automatic Distribution of Lustre Programs                                                                      | 206 |

| Reasoning about Abstract Open Systems with Generalized  Module Checking                                                     | 223 |

| Schedule-Carrying Code                                                                                                      | 241 |

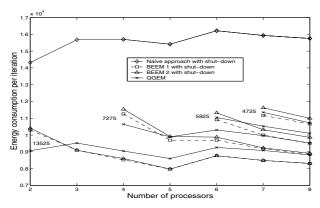

| Energy-Efficient Multi-processor Implementation of Embedded Software                                                        | 257 |

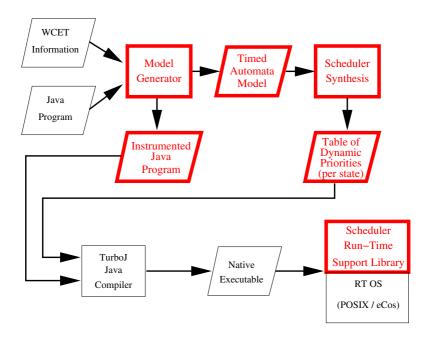

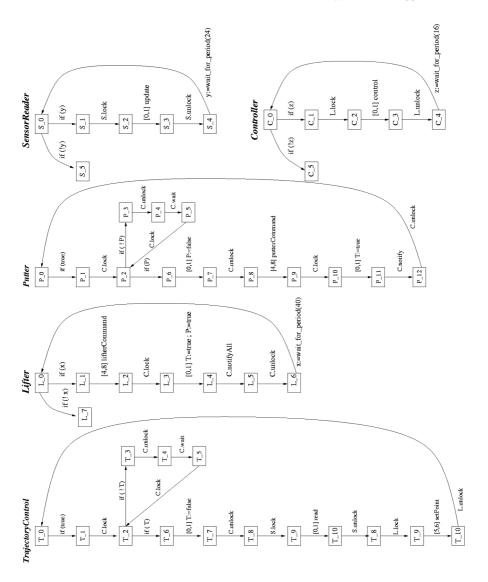

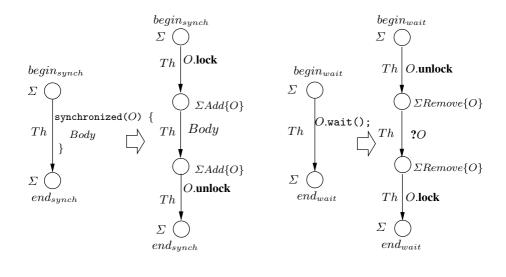

| A Methodology and Tool Support for Generating Scheduled Native<br>Code for Real-Time Java Applications                      | 274 |

| Constraint-Based Design-Space Exploration and Model Synthesis                                                               | 290 |

| Eliminating Stack Overflow by Abstract Interpretation                                                                       | 306 |

| Event Correlation: Language and Semantics                                                                                   | 323 |

| Generating Heap-Bounded Programs in a Functional Setting                                                                    | 340 |

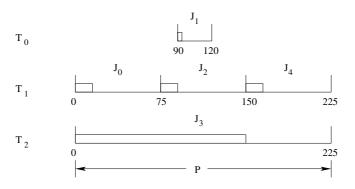

| Pre-Scheduling: Integrating Offline and Online Scheduling Techniques  Weirong Wang, Aloysius K. Mok, Gerhard Fohler         | 356 |

| Author Index                                                                                                                | 373 |

## A Probabilistic Framework for Schedulability Analysis

Alan Burns, Guillem Bernat, and Ian Broster

Real-Time Systems Research Group Department of Computer Science University of York, UK

**Abstract.** The limitations of the deterministic formulation of scheduling are outlined and a probabilistic approach is motivated. A number of models are reviewed with one being chosen as a basic framework. Response-time analysis is extended to incorporate a probabilistic characterisation of task arrivals and execution times. Copulas are used to represent dependencies.

#### 1 Introduction

Scheduling work in real-time systems is traditionally dominated by the notion of absolute guarantee. The load on a system is assumed to be bounded and known, worst-case conditions are presumed to be encountered, and static analysis is used to determine that all timing constraints (deadlines) are met in all circumstances.

This deterministic framework has been very successful in providing a solid engineering foundation to the development of real-time systems in a wide range of applications from avionics to consumer electronics. The limitations of this approach are, however, now beginning to pose serious research challenges for those working in scheduling analysis. A move from a deterministic to a probabilistic framework is advocated in this paper where we review a number of approaches that have been proposed. The sources of the limitations are threefold:

- 1. Fault tolerant systems are inheritly stochastic and cannot be subject to absolute guarantee.

- 2. Application needs are becoming more flexible and/or adaptive work-flow does not follow pre-determined patterns, and algorithms with a wide variance in computation times are becoming more commonplace.

- 3. Modern super-scalar processor architectures with features such as cache, pipelines, branch-prediction, out-of-order execution etc. result in computation times for even straight-line code that exhibits significant variability. Also, execution time analysis techniques are pessimistic and can only provide upper bounds on the execution time of programs.

Note, these characteristics are not isolated to so called 'soft real-time systems' but are equally relevant to the most stringent hard real-time application. Nevertheless, the early work on probabilistic scheduling analysis has been driven by a wish to devise effective QoS control for soft real-time systems [1,17,18,38].

In this paper we consider four interlinked themes:

- 1. Probabilistic guarantees for fault-tolerant systems

- 2. Representing non-periodic arrival patterns

- 3. Representing execution-time

- 4. Estimating extreme values for execution times.

In the third and fourth themes it will become clear that one of the axioms of the deterministic framework – a well founded notion of worst-case execution time – is not sustainable. The parameterisation of work-flow needs a much richer description than has been needed hitherto.

The above themes are discussed in Sections 3 to 5 of this paper. Before that we give a short review of standard schedulability analysis using a fixed priority scheme as the underlying dispatching policy (see Burns and Wellings [11] for a detailed discussion of this analysis). We restrict our consideration to the scheduling of single resources – processors or networks. In Section 6 we bring the discussion together and draw some conclusions.

### 2 Standard Scheduling Analysis

For the traditional fixed priority approach, it is assumed that there is a finite number (N) of tasks  $(\tau_1 \dots \tau_N)$ . Each task has the attributes of minimum inter arrival time, T, worst-case execution time, C, deadline, D and priority P. Each task undertakes a potentially unbounded number of invocations; each of which must be finished by the deadline (which is measured relative to the task's invocation/release time). All tasks are deemed to share a *critical instance* in which they are all released together; this is often taken to occur at time 0. It is important to emphasise that the standard analysis assumes that the two limits on load (minimum T and maximum T) are actually observed at run time. No compensation for average or observed T or T0 is accommodated.

We assume a single processor platform and restrict the model to tasks with  $D \leq T$ . For this restriction, an optimal set of priorities can be derived such that  $D_i < D_j \Rightarrow P_i > P_j$  for all tasks  $\tau_i, \tau_j$  [26]. Tasks may be periodic or sporadic (as long as two consecutive releases are separated by at least T). Once released, a task is not suspended other than by the possible action of a concurrency control protocol surrounding the use of shared data. A task, however, may be preempted at any time by a higher priority task. System overheads such as context switches and kernel manipulations of delay queues etc. can easily be incorporated into the model [21][10] but are ignored here.

The worst-case response time (completion time)  $R_i$  for each task  $(\tau_i)$  is obtained from the following [20][2]:

$$R_i = C_i + B_i + \sum_{j \in \mathbf{hp}(i)} \left\lceil \frac{R_i}{T_j} \right\rceil C_j \tag{1}$$

where  $\mathbf{hp}(i)$  is the set of higher priority tasks (than  $\tau_i$ ), and  $B_i$  is the maximum blocking time caused by a concurrency control protocol protecting shared data.

| Task    | P | T   | C  | D   | B | R   | Schedulable |

|---------|---|-----|----|-----|---|-----|-------------|

| $	au_1$ |   | 100 |    |     |   |     | TRUE        |

| $	au_2$ | 2 | 175 | 35 | 175 | 0 | 65  | TRUE        |

| $	au_3$ |   | 200 |    |     |   |     | TRUE        |

| $	au_4$ | 4 | 300 | 30 | 300 | 0 | 150 | TRUE        |

Table 1. Example Task Set

To solve equation (1) a recurrence relation is produced:

$$r_i^{n+1} = C_i + B_i + \sum_{j \in \mathbf{hp}(i)} \left\lceil \frac{r_i^n}{T_j} \right\rceil C_j \tag{2}$$

where  $r_i^0$  is given an initial value of 0. The value  $r^n$  can be considered to be a computational window into which an amount of computation  $C_i$  is attempting to be placed. It is a monotonically non-decreasing function of n. When  $r_i^{n+1}$  becomes equal to  $r_i^n$  then this value is the worst-case response time,  $R_i$  [10]. However if  $r_i^n$  becomes greater than  $D_i$  then the task cannot be guaranteed to meet its deadline, and the full task set is thus unschedulable. It is important to note that a fixed set of time points are considered in the analysis:  $0, r_i^1, r_i^2, ..., r_i^n$ .

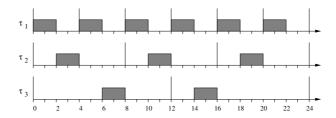

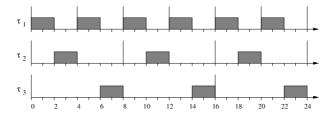

Table 1 describes a simple 4 task system, together with the worst-case response times that are calculated by equation (2). Priorities are ordered from 1, with 4 being the lowest value, and blocking times have been set to zero for simplicity. Scheduling analysis is independent of time units and hence simple integer values are used (they can be interpreted as milliseconds).

All tasks are released at time 0. For the purpose of schedulability analysis, we can assume that their behaviour is repeated every LCM, where LCM is the least common multiple of the task periods. When faults are introduced it will be necessary to know for how long the system will be executing. Let L be the lifetime of the system. For convenience we assume L is an integer multiple of the LCM. This value may however be very large (for example LCM could be 200ms, and L fifteen years!).

## 3 Probabilistic Guarantees for Fault-Tolerant Systems

In this review we restrict our consideration to transient faults. Castillo *at al* [13] in their study of several systems indicate that the occurrences of transient faults are 10 to 50 times more frequent than permanent faults. In some applications this frequency can be quite large; one experiment on a satellite system observed 35 transient faults in a 15 minute interval due to cosmic ray ions [12].

Hou and Shin [19] have studied the probability of meeting deadlines when tasks are replicated in a hardware-redundant system. However, they only consider permanent faults without repair or recovery. A similar problem was studied by Shin et al [36]. Kim et al [22] consider another related problem: the probability of a real-time controller meeting a deadline when subject to permanent faults with repair.

To tolerate transient faults at the task level will require extra computation. This could be the result of restoration and re-execution of some routine, the execution of an exception handler or a recovery block. Various algorithms have been published which attempt to maximise the available resources for this extra computation [37,35,3]. Here we consider the nature of the guarantee that these algorithms provide. Most approaches make the common homogeneous Poisson process (HPP) assumptions that the fault arrival rate is constant and that the distribution of the fault-count for any fixed time interval can be approximated using a Poisson probability distribution. This is an appropriate model for a random process where the probability of an event does not change with time and the occurrence of one fault event does not affect the probability of another such event. A HPP process depends only on one parameter, viz., the expected number of events,  $\lambda$ , in unit time; here events are transient faults with  $\lambda = 1/MTBF$ , where MTBF is the Mean Time Between transient Faults<sup>1</sup>. Per the definition of a Poisson Distribution,

$$\mathbf{Pr}_n(t) = \frac{e^{-\lambda t} (\lambda t)^n}{n!} \tag{3}$$

gives the probability of n events during an interval of duration t. If we take an event to be an occurrence of a transient fault and Y to be the random variable representing the number of faults in the lifetime of the system (L), then the probability of zero faults is given by

$$\mathbf{Pr}(Y=0) = e^{-\lambda L}$$

and the probability of at least one fault

$$\mathbf{Pr}(Y>0) = 1 - e^{-\lambda L}$$

Modelling faults as stochastic events means that an absolute guarantee cannot be given. There is a finite probability of any number of faults occurring within the deadline of a task. It follows that the guarantee must have a confidence level assigned to it and this is most naturally expressed as a probability. One way of doing this is to calculate the worst case fault behaviour that can (just) be tolerated by the system, and then use the system fault model to assign a probability to that behaviour. Two ways of doing this have been studied in detail.

- Calculate the maximum fault arrival rate that can be tolerated [9] represented by  $T_F$ , the minimum fault arrival interval.

- Calculate the maximum number of faults each task can tolerate before its deadline

[31].

The first approach is more straightforward (there is only a single parameter) and is reviewed in the following section. The basic form of the analysis is to obtain  $T_F$  from the task set, and then to derive a probabilistic guarantee from  $T_F$ . An alternative formulation

<sup>&</sup>lt;sup>1</sup> MTBF usually stands for mean time between failures, but as the systems of interest are fault tolerant many faults will not cause system failure. Hence we use the term MTBF to model the arrival of transient faults.

is to start with a required guarantee (for example, probability of fault per task release of  $10^{-6}$ ) and to then test for schedulability. This is the approach of Broster et al [6] and is outlined in Section 3.2.

#### 3.1 Probabilistic Guarantee for $T_F$

Let  $F_k$  be the extra computation time needed by  $\tau_k$  if an error is detected during its execution. This could represent the re-execution of the task, the execution of an exception handler or recovery block, or the partial re-execution of a task with checkpoints. In the scheduling analysis the execution of task  $\tau_i$  will be affected by a fault in  $\tau_i$  or any higher priority task. We assume that any extra computation for a task will be executed at the task's (fixed) priority<sup>2</sup>.

Hence if there is just a single fault, equation (1) will become [33][7]<sup>3</sup>:

$$R_i = C_i + B_i + \sum_{j \in \mathbf{hp}(i)} \left\lceil \frac{R_i}{T_j} \right\rceil C_j + \max_{k \in \mathbf{hep}(i)} (F_k)$$

(4)

where  $\mathbf{hep}(i)$  is the set of tasks with priority equal or higher than  $\tau_i$ , that is  $\mathbf{hep}(i) = \mathbf{hp}(i) \cup \{\tau_i\}$ .

This equation can again be solved for  $R_i$  by forming a recurrence relation. If all  $R_i$  values are still less than the corresponding  $D_i$  values then a deterministic guarantee is furnished.

Given that a fault tolerant system has been built it can be assumed (although this would need to be verified) that it will be able to tolerate a single isolated fault. And hence the more realistic problem is that of multiple faults; at some point all systems will become unschedulable when faced with an arbitrary number of fault events.

To consider maximum arrival rates, first assume that  $T_f$  is a known minimum arrival interval for fault events. Also assume the error latency is zero (this restriction is easily removed [9]). Equation (4) becomes [33,7]:

$$R_i = C_i + B_i + \sum_{j \in \mathbf{hp}(i)} \left\lceil \frac{R_i}{T_j} \right\rceil C_j + \left\lceil \frac{R_i}{T_f} \right\rceil \max_{k \in \mathbf{hep}(i)} (F_k)$$

(5)

Thus in interval  $(0 \ R_i]$  there can be at most  $\left\lceil \frac{R_i}{T_f} \right\rceil$  fault events, each of which can induce  $F_k$  amount of extra computation. The validity of this equation comes from noting that fault events behave identically to sporadic tasks, and they are represented in the scheduling analysis in this way [2].

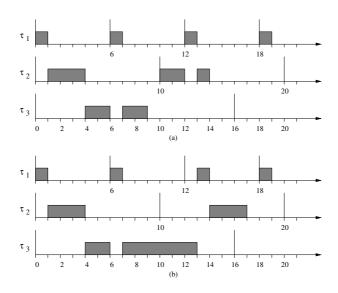

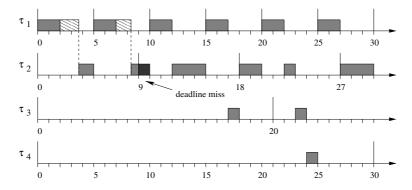

Table 2 gives an example of applying equation (5). Here full re-execution is required following a fault (ie.  $F_k = C_k$ ). Two different fault arrival intervals are considered. For one the system remains schedulable, but for the shorter interval the final task cannot be guaranteed. In this simple example, blocking and error latency are assumed to be zero. Note that for the first three tasks, the new response times are less than the shorter  $T_f$  value, and hence will remain constant for all  $T_f$  values greater than 200.

<sup>&</sup>lt;sup>2</sup> Recent results had improved the following analysis by allowing the recovery actions to be executed at a higher priority [27].

<sup>&</sup>lt;sup>3</sup> We assume that in the absence of faults, the task set is schedulable.

| Task     | P | T   | C  | D   | F  | R           | R           |

|----------|---|-----|----|-----|----|-------------|-------------|

|          |   |     |    |     |    | $T_f = 300$ | $T_f = 200$ |

| $\tau_1$ | 1 | 100 | 30 | 100 | 30 | 60          | 60          |

| $\tau_2$ | 2 | 175 | 35 | 175 | 35 | 100         | 100         |

| $\tau_3$ | 3 | 200 | 25 | 200 | 25 | 155         | 155         |

| $\tau_4$ | 4 | 300 | 30 | 300 | 30 | 275         | UNSCH       |

**Table 2.** Example Task Set -  $T_f$  = 300 and 200

**Table 3.** Example Task Set -  $T_F$  set at 275

| Task         | P | T   | C  | D   | R           |

|--------------|---|-----|----|-----|-------------|

|              |   |     |    |     | $T_F = 275$ |

| $\tau_1$     |   | 100 |    |     |             |

| $  \tau_2  $ |   | 175 |    |     |             |

| $\tau_3$     |   | 200 |    |     |             |

| $\tau_4$     | 4 | 300 | 30 | 300 | 275         |

The above analysis has assumed that the task deadlines remain in effect even during a fault handling situation. Some systems allow a relaxed deadline when faults occur (as long as faults are rare). This is easily accommodated into the analysis.

#### Limits to Schedulability

Having formed the relation between schedulability and  $T_f$ , it is possible to apply sensitivity analysis to equation (5) to find the minimum value of  $T_f$  that leads to the system being just schedulable. As indicated earlier, let this value be denoted as  $T_F$  (it is the threshold fault interval).

Sensitivity analysis [39,24,23,34] is used with fixed priority systems to investigate the relationship between values of key task parameters and schedulability. For an unschedulable system it can easily generate (using simple branch and bound techniques) factors such as the percentage by which all *C*s must be reduced for the system to become schedulable.

Similarly for schedulable systems, sensitivity analysis can be used to investigate the amount by which the load can be increased without jeopardising the deadline guarantees. Here we apply sensitivity analysis to  $T_f$  to obtain  $T_F$ .

When the above task set is subject to sensitivity analysis it yields a value of  $T_F$  of 275. The behaviour of the system with this threshold fault interval is shown in Table 3. A value of 274 would cause  $\tau_4$  to miss its deadline.

In the paper cited earlier for this work, formulae are derived for the probability that during the lifetime of the system, L, no two faults will be closer than  $T_F$ . This is denoted by  $Pr(W < T_F)$ ; where W denotes the actual (unknown) minimum inter-fault gap. Of course,  $Pr(W < T_F)$  is equivalent to  $1 - Pr(W \ge T_F)$ . The exact formulation is

$$Pr(W \ge T_F) = \sum_{n=0}^{\infty} P_{n, (T_F/L)} e^{-\lambda L} \frac{(\lambda L)^n}{n!}$$

$$= e^{-\lambda L} \left\{ 1 + \lambda L + \sum_{n=2}^{\left\lceil \frac{L}{T_F} \right\rceil} \left( 1 - (n-1) \left( \frac{T_F}{L} \right) \right)^n \frac{(\lambda L)^n}{n!} \right\}$$

$$= e^{-\lambda L} \left\{ 1 + \lambda L + \sum_{n=2}^{\left\lceil \frac{L}{T_F} \right\rceil} \frac{\lambda^n}{n!} \left( L - (n-1)T_F \right)^n \right\}$$

(6)

this leads to

$$Pr(W \ge T_F) = e^{-\lambda L} \left\{ 1 + \lambda L + \sum_{n=2}^{\infty} \frac{(\lambda L - (n-1)\lambda T_F)_+^n}{n!} \right\}$$

(7)

Fortunately upper and lower bands can also be derived.

**Theorem 1.** If  $L/(2T_F)$  is a positive integer then

$$Pr(W < T_F) < 1 + \left[e^{-\lambda T_F} (1 + \lambda T_F)\right]^{\frac{L}{T_F} - 1} - 2\left[e^{-2\lambda T_F} (1 + 2\lambda T_F)\right]^{\frac{L}{2T_F}}$$

**Theorem 2.** If  $L/(2T_F)$  is a positive integer then

$$Pr(W < T_F) > 1 - \left[e^{-\lambda T_F} \left(1 + \lambda T_F\right)\right]^{\frac{L}{T_F}}$$

which gives rise to the approximations

**Corollary 1.** An approximation for the upper bound on  $Pr(W < T_F)$  given by Theorem 1 is  $\frac{3}{2}\lambda^2 LT_F$ , provided that  $\lambda T_F$ ,  $\lambda^2 LT_F$  are small, and  $L\gg T_F$ .

**Corollary 2.** An approximation for the lower bound on  $Pr(W < T_F)$  given by Theorem 2 is  $\frac{1}{2}\lambda^2 LT_F$ , provided only that  $\lambda T_F$ ,  $\lambda^2 LT_F$  are small.

The important upper bound approximation of Corollary 1 can be written in the form  $\frac{3}{2}(\lambda L)(\lambda T_F)$ . It will often be the case that  $\lambda T_F < 10^{-2}$ ; indeed this constraint allowed the approximations to deliver useful values. But  $\lambda L$  can vary quite considerably from  $10^{-2}$  or less in friendly environments to  $10^3$  or more in long-life, hostile domains.

The example introduced in earlier had a  $T_F$  value of 275ms. Table 4 gives the upper bound on the probability guarantee for various values of  $\lambda$  and L (in seconds).

A typical outcome of this analysis is that in a system that has a non-stop run-time (L) of 10 hours with a mean time between transient faults of 1000 hours and a tolerance of faults that do not appear closer than 1/100 of an hour, the probability of missing a deadline is upper bounded by  $1.5\times10^{-7}$ . A lower bound is also derived (Corollary 4) and this yields a value of  $0.5\times10^{-7}$ . For these parameters the exact analysis produces a value very close to  $1.0\times10^{-7}$ .

When  $\lambda L < 10^{-2}$ ,  $\lambda L$  approximates the probability of any fault happening during the mission of duration L. So,  $\frac{2}{3}(\lambda T_F)^{-1}$  represents the gain in reliability that is achieved by the use of fault tolerance, under the other assumptions stated. For example, in Table 4, when  $\lambda = 10^{-2}$  and L = 1 the gain is approximately  $10^6$ .

|          |                      | λ                    |                       |

|----------|----------------------|----------------------|-----------------------|

| L        | 1                    | $10^{-2}$            | $10^{-4}$             |

|          |                      |                      | $1.1 \times 10^{-12}$ |

|          |                      |                      | $1.1 \times 10^{-11}$ |

| $10^{2}$ | $1.1 \times 10^{-2}$ | $1.1 \times 10^{-6}$ | $1.1 \times 10^{-10}$ |

| $10^{4}$ | 1                    | $1.1 \times 10^{-4}$ | $1.1 \times 10^{-8}$  |

Table 4. Upper bound on Non-Schedulability due to Faults

#### 3.2 Scheduling Analysis for Probabilistic Events

In contrast to the above approach Broster et al [6] produce a response time profile that is a direct result of the probabilisitic fault model. They do not assume a single  $T_F$  value. Their analysis was originally derived for CAN scheduling but is generalised here. Rather than consider the lifetime of the system, L, the analysis is formulated in terms of the likelihood of failure per execution of the task. There is an obvious straightforward relationship between these two formulations.

It was noted earlier that standard response analysis for fixed priority scheduling looks at a series of time points,  $0, r_i^1, r_i^2, ..., r_i^n$ . (We shall ignore the task subscript in the following description). This approach susumes no faults. It is possible to generalise the scheme by replacing the single point  $r^1$  by a series of points that are obtained by assuming one fault, two faults etc. That is  $r(0)^1, r(1)^1, r(2)^1, ..., r(m)^1$  (with  $r(0)^1 = r^1$ ). The fault model (eg. Poisson) is able to provide a value for the probability of s faults in  $r(s)^1$  – see equation(3).

Once all probabilities are obtained that are greater then the required guarantee (eg.  $10^{-6}$ ) the sequence is terminated and for each value of  $r(s)^1$  a set of secondary points are obtained  $r(s,q)^2$  with the second parameter, q, being the number of faults in the interval  $[r(s)^1,r(s,q)^2),q=0,1,2,...$  This process is repeated and at each interaction, events (faults) with a likelihood below the threshold of interest are ignored. Although the overall search space is potentially large, the trimming that occurs due to dismissing rare events, leads to a scheme has been shown to be tractable for real sized problems. Once all sequences terminate, deadlines are checked and a probability distribution for response times is obtained.

Scheduling Analysis for Required Probabilistic Guarantee. An alternative way of formulating the question of a probabilistic guarantee of schedulability is to calculate the worst-case response time when fault occurrences, below the threshold of interest, are ignored. Note this is not the same question as that addressed by Broster. To answer this formulation of the question is much easier as only a single iteration of the scheduling equation is needed. First equation (4) is solved assuming zero faults (let this value be represented by R(0) – we again ignore the task subscript). Then the fault model, the threshold and this value R(0) are used to estimate the number of faults (of interest) in the interval. Let this value be  $S_1$ . From equation (4) we can now calculate a new value for response time,  $R(S_1)$ :

$$R_i(S_1) = C_i + B_i + \sum_{j \in \mathbf{hp}(i)} \left\lceil \frac{R_i}{T_j} \right\rceil C_j + S_1 \max_{k \in \mathbf{hep}(i)} (F_k)$$

(8)

The number of faults of interest in  $R(S_1)$  is then calculated. If this new value,  $S_2$ , is equal to  $S_1$  then the formulation is stable and  $R(S_1)$  is the worst case response time. Alternatively equation (8) is solved for  $S_2$  and the process continues until either stability is obtained or a response time greater than deadline is calculated and unschedulability is proclaimed.

To illustrate the approach consider the small example given earlier for the other approach. If we set the threshold value to  $10^{-6}$  and assume  $\lambda$  is obtained from a mean time between errors of 0.1 seconds then the same response time give in Table 3 are observed (eg. 60, 100, 155 and 275).

Note that the above analysis is relatively straightforward when a Poisson derived fault model is assumed. Nevertheless, the framework can still be used if other arrival distributions are more appropriate.

#### 3.3 Summary

The schemes reviewed in this section all have a common theme. Scheduling approaches are used to maximise the effective resources that can be made available, when required, for fault tolerance. Then limits to schedulability are derived in conjuction with the probability of those limits being observed during execution. This furnishes the probabilistic guarantee. Alternatively, a standard yes/no guarantee is obtained while faults below a threshold of likelihood are ignored.

## 4 Probabilistic Guarantees with Non-periodic Work

Initially scheduling analysis assumed a purely periodic work flow [28]. The sporadic jobs were incorporated by assuming a minimum arrival time, that in the worst case was exhibited by the system. In effect a sporadic job behaved exactly the same as a periodic one. Response time analysis, as outlined in Section 2 can actually deal with a much more general model of non-periodic work. Let  $A_k(t)$  be defined to be a function that delivers the maximum number of arrivals of task k in any interval [0,t). Then equation (1) becomes

$$R_i = C_i + B_i + \sum_{j \in \mathbf{hpp}(i)} \left\lceil \frac{R_i}{T_j} \right\rceil C_j + \sum_{k \in \mathbf{hpn}(i)} A_k(R_i) C_k \tag{9}$$

where  $\mathbf{hpp}(i)$  is now the set of higher priority periodic tasks, and  $\mathbf{hpn}(i)$  the set of higher priority non-periodic tasks.

Although a useful generalisation, equation (9) is still a deterministic one. It assumes that the worst-case number of arrivals of all sporadics tasks will occur with probability one. To deal with non-periodic tasks that follow a stochastic model a different framework is needed. First, some form of probabilistic density function will be needed for all sources

of sporadic work. If nothing is known about the arrival pattern of work then clearly no guarantee, not even a probabilistic one, can be given. One method of incorporating this stochastic work load is to use the same approach as for fault tolerance. After all, faults handling routines are, from a scheduling point of view, just one form of non-periodic work. The approach outlined in Section 3.2 can then be applied.

A probability threshold for the system must be defined. This is the value below which events are sufficiently rare to be ignored. Let  $\rho$  be this threshold value. We redefined the function A given earlier in this section as follows:  $A_k(\rho,t)$  is the number of arrival events in any interval of length t with a probability of more than  $\rho$ . So  $A_k(10^{-6},30)$ , for example, would give the result 2 if the probability of 3 or more arrivals in 30 time units is less than  $10^{-6}$  (and the probability of 2 is more than this value). Equation (9) then becomes:

$$R_i = C_i + B_i + \sum_{j \in \mathbf{hpp}(i)} \left\lceil \frac{R_i}{T_j} \right\rceil C_j + \sum_{k \in \mathbf{hpn}(i)} A_k(\rho, R_i) C_k$$

(10)

This approach contains some explicit assumptions that would need to be clarified. For example, it assumes each source of arrivals is independent of each other; also that the computation time of the job is independent of the arrival behaviour. The existence of correlations would complicate the analysis – but pessimistic assumptions may be relatively straightforward to incorporate (see later discussion on the use of Copulas).

Care must of course be taken with choosing the probability threshold for the system. If an application is, by its specification, meant to deal with rare events then the threshold must be chosen so that such events (at least one in any small interval) are always incorporated into the run-time behaviour that is being analysed.

## 5 Representing Execution Time

The above discussions have generalised the notion of work flow by allowing the arrival of work to be described stochastically. However the worst-case resource requirement of each job is still represented by a single parameter C. This represents the maximum processor (resource) time needed by the job on each and every arrival. In developing a general framework for scheduling analysis, where application code and processor behaviour combined to produce a rich execution profile, it is not surprising that this single parameter approach is becoming limited in its application. Even a two (average and worst-case) or three (add minimum) parameter scheme is far from adequate.

In other works [8,16,4] we have argued that it is now inadequate to use analysis alone to obtain a single worst-case execution time (WCET) value. Rather a combination of analysis and measurement must be used to obtain a probabilistic representation of the entire execution profile of the task. Moreover, this probability density function must extend beyond observed data to predict the likelihood of experiencing, during the real execution of the system, extreme (large) values for execution time. Data obtained from measurement of relatively straightforward code illustrates two general characteristics of execution time profiles (let *O* be the maximum observed value during meansurement).

- Large observed values for computation time may be sufficiently rare that for non-hard systems it would be inappropriate for any schedulability test to assume this value for every task's execution (ie. O is too large to use).

- Large observed values for computation time may not represent the worst-case that will be experienced during real execution, and extrapolations beyond observed values will be needed for some hard real-time systems (ie. O is too small to use).

The alternative to simple parameterisation is to model execution time as a random variable following some probability distribution. These distributions (execution time profiles) being derived from measurement. But the granularity of measurement remains an open issue. Three levels are possible:

- 1. The basic block a sequence of instructions.

- 2. The task which consists of a number of basic blocks.

- 3. The system which consists of a number of tasks.

If measurement is used at the task level then knowledge about the structure of the task is being ignored, however uncertainties arising from the interactions of basic blocks are being sampled. If analysis is used at the task level (with measurements only being done for basic blocks) then the rules for combining the execution time profiles need to be articulated. A similar trade-off exists at the system level.

In the work we have undertaken, we have used measurement only at the basic block level and hence we must address the issue of how to combine probability distributions. If independence could be assumed then standard statistical methods could be applied. Unfortunately there seems to be ample evidence that this assumption would be overtly optimistic. A series of basic blocks may be strongly correlated. Moreover a series of task executions within a schedule may also be dependent upon one another. Indeed the execution of the same task, one or more times, within the response time of a lower priority task may exhibit a strong correlation. These may be positive (a long execution time is more likely to be followed by another large one) or negative (long will induce a short one next time).

### 5.1 Use of Copulas

Copulas are a general mathematical tool to construct multivariate distributions and to investigate dependence structures between random variables [32]. A copula is basically a joint distribution function with uniform marginals. The main feature is that they allow one to separate the marginal distributions from the dependency between the two random variables, therefore given a joint probability distribution it is possible to characterize it uniquely with the marginal distributions and a copula. Similarly, given two marginal distributions and a copula, it is possible to derive the joint distribution and this is unique.

The importance is that the copula captures the *dependence structure* between random variables. So given two joint distributions with different marginal distributions but that capture the same dependency process, they would have the same copula.

There are two additional results of importance for this analysis, the first one is that the set of copulas is a partially ordered set and there exist two special copulas, called the lower

and upper Fréchet bounds that characterize the maximum and minimum dependence between random variables.

The problem of timing analysis can be formulated as follows, if X and Y are two random variables that represent the execution time of two blocks of code with respective distribution functions  $F_X(t)$  and  $F_Y(t)$ , we want to determine the distribution of Z = X + Y which is the execution time of X followed by Y,  $F_Z(t)$ . If X and Y are independent, the probability density function of Z corresponds to the standard convolution of the probability density functions of X and Y. However, if this hypothesis is not correct then we can use the theory of copulas to construct  $F_Z(t)$ .

If the joint distribution is known, (or its copula) then the distribution of Z is a straightforward generalisation of the convolution but using the joint distribution instead. More importantly, if the dependency is not known, then it is possible to find upper and lower bounds of the distribution function for *any* possible dependency between the marginal distributions [5,29,14]. Some generalisations of these results allow to tighten even more these bounds if partial knowledge of the dependence is known.

#### 5.2 Representing Extreme Execution Times

It was noted earlier that for some hard real-time systems execution time values beyond what have been observed during tests need to be taken into account if very low levels of failure are to be tolerated. One means of addressing this issue is to apply the branch of statistics concerned with extreme values. One of the three extreme value distributions is used to 'fit' the data and then give predictions beyond the observed data range. We have had some success [16] in fitting the Gumble distribution but it is still not clear if this is a general purpose technique. What this approach provides is a probability distribution for the worst-case value for a task's execution. One useful result of this study is that a collection of tasks has a bounded behaviour. Let  $C_1...C_N$  be the worst-case times derived from the above approach with probability threshold  $\rho$ ; then the sequential execution of each task will have a total expected execution time of  $C_1 + C_2 + C_3 + ... + C_N$  with probability bound  $\rho$ .

## 6 Other Relevant Work on Probabilistic Analysis

There have been some other approaches using probabilistic methods in real-time systems. The work of Diaz et.al. [15] computes probability distributions of the response times of entirely periodic (fixed release times) task systems with random execution times. The work relies on the independence of the execution times of the different tasks. The work improves on an earlier work by Gardner et.al. [18]. The works of Nissanke [25] and Eles [30] also tackle this problem. However, none of these approaches address the issue of extreme distributions or dependencies between execution times or task arrivals.

#### 7 Conclusion: A Probabilistic Framework

Bringing together the above approaches we are able to postulate one means of constructing a scheduling framework that can deal with stochastic parameterisation of work flow. The following are the main components of such a framework.

- 1. All tasks have an arrival pattern expressed as  $A(\rho, t)$  the number of instances of the task likely to occur in any interval of length t, where the probability of greater than  $A(\rho, t)$  occurring is less than  $\rho$ .

- 2. All tasks have an execution profile derived that extends beyond the data observed during test.

- 3. A threshold probability is defined for the system. Events (task arrivals or execution times) with a likelihood of occurring less than this threshold are ignored. The threshold could be expressed as a likelihood of failure per execution of any task of interest.

- 4. A worst-case response time of each task is calculated from the above data as follows:

- An initial estimate,  $R_0$ , is obtained by assuming all tasks arrive once with execution times derived from their profiles and  $\rho$ .

- The number of tasks arriving in  $R_0$  is derived (using  $A(\rho, R_0)$ ) and any dependency relationships).

- A conservative copula is used to combine the execution profiles of those jobs.

- A new value for  $R_0$  (i.e.  $R_1$ ) is obtained by using the threshold probability value on this derived distribution.

- Repeat until a stable value of R is obtained (or R expands beyond the task's deadline).

It would be at least theoretically possible to vary the probability threshold to derive a relation between response time and this threshold.

In conclusion, we have argued in support of the developed the notion of a probabilistic assessment of schedulability and shown how it can be derived from the stochastic behaviour of the work that the real-time system must accomplish. Many aspects of this framework require significant further study, and we aim to continue with this line of investigation.

#### References

- A.K. Atlas and A. Bestavros. Statistical rate monotonic scheduling. In *Proceedings of the* 19th IEEE Real-Time Systems Symposium, Madrid, Spain, pages 123–132. IEEE Computer Society Press, 1998.

- N. C. Audsley, A. Burns, M. Richardson, K. Tindell, and A. J. Wellings. Applying new scheduling theory to static priority pre-emptive scheduling. *Software Engineering Journal*, 8(5):284–292, 1993.

- G. Bernat and A. Burns. New results on fixed priority aperiodic servers. In 20th IEEE Real-Time Systems Symposium, Phoenix. USA, December 1999.

- G. Bernat, A. Colin, and S. M. Petters. WCET analysis of probabilistic hard real–time systems. In *Proceedings of the 23rd Real-Time Systems Symposium RTSS 2002*, pages 279–288, Austin, Texas, USA, 2002.

- 5. G. Bernat and M. Newby. Probabilistic WCET analysis, an approach using copulas. Technical report, Department of Computer Science University of York, Technical Report, 2003.

- 6. I. Broster, A. Burns, and G. Rodríguez-Navas. Probabilistic analysis of CAN with faults. In *Proceedings of the 23rd Real-time Systems Symposium*, Dec 2002.

- 7. A. Burns, R. I. Davis, and S. Punnekkat. Feasibility analysis of fault-tolerant real-time task sets. *Euromicro Real-Time Systems Workshop*, pages 29–33, June 1996.

- 8. A. Burns and S. Edgar. Predicting computation time for advanced processor architectures. In *Proceedings 12th EUROMICRO conference on Real-time Systems*, 2000.

- A. Burns, S. Punnekkat, L. Strigini, and D.R. Wright. Probabilistic scheduling guarantees for fault-tolerant real-time systems. In *Proceedings of the 7th International Working Conference* on Dependable Computing for Critical Applications. San Jose, California, pages 339–356, 1999.

- 10. A. Burns and A. J. Wellings. Engineering a hard real-time system: From theory to practice. *Software-Practice and Experience*, 25(7):705–26, 1995.

- 11. A. Burns and A. J. Wellings. *Real-Time Systems and Programming Languages*. Addison Wesley Longman, 3rd edition, 2001.

- 12. A. Campbell, P. McDonald, and K. Ray. Single event upset rates in space. *IEEE Transactions on Nuclear Science*, 39(6):1828–1835, December 1992.

- 13. X. Castillo, S.P. McConnel, and D.P. Siewiorek. Derivation and Calibration of a Transient Error Reliability Model. *IEEE Transactions on Computers*, 31(7):658–671, July 1982.

- 14. H. Cossette, M. Denuit, and E. Marceau. Distributional bounds for functions of dependent risks. Technical report, Bulletin suisse des actuaires., 2001.

- J.L. Diaz, D. F. García, K. Kim, C.-G. Lee, L.L. Bello, J.M. Lopez, S.L. Min, and O. Mirabella. Stochastic analysis of periodic real-time systems. In 22nd IEEE Real-Time Systems Symposium., Austin, TX. USA, 2002.

- 16. S. Edgar and A. Burns. Statistical analysis of WCET for scheduling. In *Proceedings IEEE Real-Time Systems Symposium*, 2001.

- 17. M. K. Gardner. *Probabilistic Analysis and Scheduling of Critical Soft Real-time Systems*. PhD thesis, University of Illinois, Computer Science, Urbana, Illinois, 1999.

- 18. M. K. Gardner and J.W. Lui. Analysing stochastic fixed-priority real-time systems. In *Proceedings of the 5th International Conference on Tools and Algorithms for the Construction and Analysis of Systems*, 1999.

- 19. C.-J. Hou and K. G. Shin. Allocation of periodic task modules with precedence and deadline constraints in distributed real-time systems. *IEEE Transactions on Computers*, 46(12):1338–1356, 1997.

- 20. M. Joseph and P. Pandya. Finding response times in a real-time system. *BCS Computer Journal*, 29(5):390–395, 1986.

- 21. D.I. Katcher, H. Arakawa, and J.K. Strosnider. Engineering and analysis of fixed priority schedulers. *IEEE Trans. Softw. Eng.*, 19, 1993.

- 22. H. Kim, A.L.White, and K. G.Shin. Reliability modeling of hard real-time systems. In *Proceedings 28th Int. Symp. on Fault-Tolerant Computing (FTCS-28)*, pages 304–313. IEEE Computer Society Press, 1998.

- M. H. Klein, T. A. Ralya, B. Pollak, R. Obenza, and M. G. Harbour. A Practitioner's Handbook for Real-Time Analysis: A Guide to Rate Monotonic Analysis for Real-Time Systems. Kluwer Academic Publishers, 1993.

- J.P. Lehoczky, L. Sha, and V. Ding. The rate monotonic scheduling algorithm: Exact characterization and average case behavior. Tech report, Department of Statistics, Carnegie-Mellon, 1987.

- A. Leulseged and N. Nissanke. Stochastic analysis of periodic real-time systems. In 9th Intl. Conf. on Real-Time and Embeded Computing Systems and applications (RTCSA 2003), Taiwan, 2003.

- 26. J.Y.T. Leung and J. Whitehead. On the complexity of fixed-priority scheduling of periodic, real-time tasks. *Performance Evaluation (Netherlands)*, 2(4):237–250, 1982.

- 27. G. Lima and A. Burns. An optimal fixed-priority assignment algorithm for supporting fault-tolerant hard real-time systems. *IEEE Transactions on Computer Systems (to appear)*, 2003.

- 28. C.L. Liu and J.W. Layland. Scheduling algorithms for multiprogramming in a hard real-time environment. *JACM*, 20(1):46–61, 1973.

- 29. G.D. Makarov. Estimates for the distribution function of a sum of two random variales when the marginal distributions are fixed. *Theory Probab. Appli.*, 26:803–806, 1981.

- S. Manolache, P. Eles, and Z. Peng. Memory and time efficient schedulability analysis of task sets with stochastic execution time. In *Proceedings 13th EUROMICRO conference on Real-time Systems*, 2001.

- 31. N. Navet, Y.-Q.Song, and F. Simonot. Worst-case deadline failure probability in real-time applications distributed over controller area network. *Journal of Systems Architecture*, 46(1):607–617, 2000.

- 32. R.B. Nelsen. An introduction to Copulas. Springer, 1998.

- 33. S. Punnekkat. *Schedulability Analysis for Fault Tolerant Real-time Systems*. PhD thesis, Dept. Computer Science, University of York, 1997.

- 34. S. Punnekkat, R. Davis, and A. Burns. Sensitivity analysis of real-time task sets. In *Proceedings of the Conference of Advances in Computing Science ASIAN '97*, pages 72–82. Springer, 1997.

- 35. S. Ramos-Thuel and J.P. Lehoczky. On-line scheduling of hard deadline aperiodic tasks in fixed-priority systems. In *Proceedings of 14th IEEE Real-Time Systems Symposium*, pages 160–171, December 1993.

- 36. K. G. Shin, M. Krishna, and Y. H. Lee. A unified method for evaluating real-time computer controllers its application. *IEEE Transactions on Automatic Control*, 30:357–366, 1985.

- 37. M. Silly, H. Chetto, and N. Elyounsi. An optimal algorithm for guaranteeing sporadic tasks in hard real-time systems. In *Proceedings 2nd IEEE Symposium on Parallel and Distributed Systems*, pages 578–585, 1990.

- 38. T.S. Tia, Z. Deng, M. Shankar, M. Storch, J. Sun, L.C. Wu, and J.S. Liu. Probabilisitc performance guenrantee for real-time tasks with varying computation times. In *Proceedings of the Real-Time Technology and Applications Symposium*, pages 164–173, 1995.

- 39. S. Vestal. Fixed Priority Sensitivity Analysis for Linear Compute Time Models. *IEEE Transactions on Software Engineering*, 20(4):308–317, April 1994.

## **Resource-Efficient Scheduling for Real Time Systems**

Kim G. Larsen

BRICS\*, Aalborg University Denmark Fredrik Bajers Vej 7, 9220 Aalborg Ø – Denmark kgl@cs.auc.dk

#### 1 Introduction

For embedded systems efficient utilization of resources is an acute problem arising from the increasing computational demands in all sorts of applications. The consumers constantly demand better functionality and flexibility of embedded products which imply an increase in the resources needed for their realization. In several areas – e.g. portable devices such as PDAs, mobile phones and laptops as well as mission critical systems such as space applications – the ability to design resource efficient solutions is crucial.

Our own work in this area include development and applications of the real-time verification tool UPPAAL to the modeling, analysis and synthesis of resource-efficient and -optimal schedules for real-time systems. Whereas (hard) timeliness and resource-efficiency may be seen as conflicting goals, this approach allows for both goals to be achieved.

## 2 Verification Using UPPAAL

UPPAAL [20] is an integrated tool environment for modeling, simulating and verification of real-time systems, developed jointly by BRICS at Aalborg University in Denmark and by DoCS at Uppsala University in Sweden. The modeling language of UPPAAL supports model checking safety and (bounded) liveness properties of systems that can be modeled as a collection of timed automata communicating through (broadcast as well as binary) channels or shared variables. Typical application areas include real-time controllers where timely execution of a number of (periodic or sporadic) tasks is controlled by a particular scheduling policy. Given timed automata models of the tasks, the scheduler(s) as well as the real-time environment of the control systems the verification engine of UPPAAL may validate (or refute) the correctness and resouce requirements of the particular scheduling policy applied.

In a number of papers [13,16,11] this approach has been applied to systems controlled by LEGO® MINDSTORM<sup>TM</sup> bricks. Here the UPPAAL models of task are automatically synthesised from the RCX<sup>TM</sup> programs together with a model of the (round-robin) scheduling policy applied. The significant difference in the frequency by which changes occur in the scheduler (numerous samples per second) and in the environment (possibly seconds between changes) causes a fragmentation of the symbolic state space of UPPAAL.

<sup>\*</sup> Basic Research in Computer Science (www.brics.dk), funded by the Danish National Research Foundation.

As a remedy an exact acceleration technique has been developed [12] and demonstrated efficient on a number of examples.

## 3 Optimal Scheduling Using UPPAAL

In more recent work UPPAAL has been applied to the *synthesis* of the scheduling policy itself. This work was initiated during the now terminated ESPRIT project VHS [21] and is continuing within the ongoing IST project AMETIST [2]. Modeling the tasks to be scheduled, the constraining, shared resources involved as well as timing assumptions of the environment allows the scheduling problem to be stated as a (time-bounded) reachability question. The (possible) diagnostic trace provided by UPPAAL offers a valid schedule to the problem. Extending UPPAAL with mechanisms for guiding the exploration has proved extremely successful in obtaining feasible solutions to industrial scheduling problems including the synthesis of production schedules for a the Steel Production Plant SIDMAR in Ghent, Belgium [10,14].

Often one want not just a an arbitrary valid schedule but rather a schedule which is *optimal* with respect to some suitable cost measure (e.g. in terms of total elapsed timed or total power consumption). For this purpose an extension of the timed automata model with a notion of *cost* was introduced in [5]: each action transition has an associated price, and likewise, each location has an associate rate giving the increase in cost for delaying on time-unit. In [5], and independently in [1], computability of minimal-cost reachability was demonstrated based on a cost-extension of the classical notion of regions. Later, in [6,17], efficient zone-based algorithms for computing minimum-time respectively minimum-cost reachability has been given and applied to a range of optimal scheduling problems including job shop scheduling problems and aircraft landing problems. The optimization criteria distinguish scheduling algorithms from classical, full state space exploration model checking algorithms. In the UPPAAL implementation [3] they are are used together with, for example, branch-and-bound techniques to prune parts of the search space that are guaranteed not to contain optimal solutions.

Current research considers efficient computation of optimal *infinite* schedules as well as optimal *dynamic* schedules (i.e. optimal under uncertainty or in the presence of uncontrollable behaviour).

## 4 Applications

Emphasis in the talk will be given to the application of UPPAAL to two industrial scheduling problems focusing on memory utilization and power/energy consumption respectively.

The first case study [4] is provided by Terma A/S who is developing and producing radar sensor equipment. The case study, conducted in the IST AMETIST project, focuses on the memory interface of the video processing board of a radar sensor system used for ground surveillance at airports and for coastal surveillance. The task of the memory interface is to control access to a single memory bus used by 9 different (buffered) data streams. A valid scheduler must guarantee that none of the data streams are ever interrupted, and efficiency is measured in the requirement to buffer sizes. During the first

year of AMESTIST several models has been developed including models in UPPAAL [19], where verification has confirmed the validity of the scheduling principle applied by Terma today. Also, the developed models have lead to identification of a memory-optimal, new scheduling principle [22].

The second case study focuses on Dynamic Voltage Scaling, which appears as one of the most promising methods for reducing energy consumption. The principle consists in dynamically adjusting the clock-cycle length as well as the supply voltage depending on the actually task load in the system. However, optimality depends highly on the concrete hardware platform as well as the type of applications. Within the newly formed Danish center for embedded software systems, CISS [8], and in collaboration with Analog Devices various DVS scheduling principles are modeled, simulated and analyzed, with Analog Devices Blackfin DSP processor (ADSP-21535 EZ-KIT Lite) as ultimate target.

#### References

- R. Alun, S. La Torre, and G. J. Pappas. Optimal paths in weighted timed automata. To appear in HSCC2001.

- 2. The AMETIST home page. http://ametist.cs.utwente.nl.

- 3. G. Behrmann. Guiding and cost optimizing uppaal. Web-page, 2002.

- G. Behrmann, S. Bernicot, T. Hune, K.G. Larsen, S. Lecamp, and A. Skou. Case study 2: A memory interface for radar systems. Deliverable for AMETIST.

- 5. Gerd Behrmann, Ansgar Fehnker, Thomas Hune, Kim G. Larsen, Paul Pettersson, Judi Romijn, and Frits Vaandrager. Minimum-Cost Reachability for Priced Timed Automata. In Maria Domenica Di Benedetto and Alberto Sangiovanni-Vincentelli, editors, *Proceedings of the 4th International Workshop on Hybrid Systems: Computation and Control*, number 2034 in Lecture Notes in Computer Sciences, pages 147–161. Springer-Verlag, 2001.

- Gerd Behrmann, Ansgar Fehnker, Thomas Hune, Kim G. Larsen, Paul Pettersson, and Judi Romijn. Efficient Guiding Towards Cost-Optimality in UPPAAL. In T. Margaria and W. Yi, editors, *Proceedings of the 7th International Conference on Tools and Algorithms for the* Construction and Analysis of Systems, number 2031 in Lecture Notes in Computer Science, pages 174–188. Springer–Verlag, 2001.

- Johan Bengtsson, Kim G. Larsen, Fredrik Larsson, Paul Pettersson, Yi Wang, and Carsten Weise. New Generation of UPPAAL. In *Int. Workshop on Software Tools for Technology Transfer*, June 1998.

- 8. The CISS home page. http://ciss.auc.dk.

- 9. H. Dierks, G. Behrmann, and K.G. Larsen. Solving planning problems using real-time model checking (translating pddl3 into timed automata). 2003.

- 10. A. Fehnker. Citius, Vilius, Melius Guiding and Cost-Optimality in Model Checking of Timed and Hybrid Systems. PhD thesis, KUN Nijmegen, 2002.

- 11. M. Hendriks. Translating uppaal to not quite c. Technical Report 8, Nijmegen University, 2001

- M. Hendriks and K. G. Larsen. Exact acceleration of real-time model checking. In E. Asarin,

O. Maler, and S. Yovine, editors, *Electronic Notes in Theoretical Computer Science*, volume 65. Elsevier Science Publishers, April 2002.

- 13. Thomas Hune. Modelling a Real-Time Language. In proceedings of 4th Workshop on Formal Methods for Industrial Critical Systems, FMICS'99., 1999.

- 14. Thomas Hune, Kim G. Larsen, and Paul Pettersson. Guided Synthesis of Control Programs Using Uppaal. In Ten H. Lai, editor, *Proc. of the IEEE ICDCS International Workshop on Distributed Systems Verification and Validation*, pages E15–E22. IEEE Computer Society Press, April 2000.

- 15. Thomas Hune, Kim G. Larsen, and Paul Pettersson. Guided Synthesis of Control Programs using Uppaal. *Nordic Journal of Computing*, 8(1):43–64, 2001.

- 16. Torsten K. Iversen, Kåre J. Kristoffersen, Kim G. Larsen, Morten Laursen, Rune G. Madsen, Steffen K. Mortgensen, Paul Pettersson, and Chris B. Thomasen. Model-Checking Real-Time Control Programs. To be published in Proceedings of Euromicro 2000.

- 17. Kim G. Larsen, Gerd Behrmann, Ed Brinksma, Ansgar Fehnker, Thomas Hune, Paul Pettersson, and Judi Romijn. As cheap as possible: Efficient cost-optimal reachability for priced timed automata. In G. Berry, H. Comon, and A. Finkel, editors, *Proceedings of CAV 2001*, number 2102 in Lecture Notes in Computer Science, pages 493–505. Springer–Verlag, 2001.

- 18. Kim G. Larsen, Gerd Behrmann, Ed Brinksma, Ansgar Fehnker, Thomas Hune, Paul Pettersson, and Judi Romijn. As cheap as possible: Efficient cost-optimal reachability for priced timed automat. In G. Berry, H. Comon, and A. Finkel, editors, *Proceedings of CAV 2001*, number 2102 in Lecture Notes in Computer Science, pages 493–505. Springer–Verlag, 2001.

- 19. E. Seshauskaire and M. Mikucionis. Memory interface analysis using the real-time model checker uppaal. Deliverable for AMETIST.

- 20. The UPPAAL home page. http://www.uppaal.com.

- 21. The VHS home page. http://www-verimag.imag.fr//VHS/main.html.

- 22. Gera Weiss. Optimal Scheduler for a Memory Card. Research report, Weizmann, 2002.

## **Emerging Trends in Adaptive Middleware and Its Application to Distributed Real-Time Embedded Systems**

Joseph P. Loyall

BBN Technologies Cambridge, MA jloyall@bbn.com

**Abstract.** Embedded systems have become prevalent in today's computing world and more and more of these embedded systems are highly distributed and network centric. This adds increasing degrees of resource contention, unpredictability, and dynamism to software that has traditionally been designed with resources being provisioned statically and for the worst case. This paper describes the research that we've been doing in the development of middleware for QoS adaptive systems – an extension to standard off-the-shelf distributed object middleware – and its application to two military distributed real-time embedded systems. These real-world evaluations of the technology then motivate a discussion of the next directions in which we are taking this research.

#### 1 Introduction

Over 99% of all microprocessors are now used for embedded systems [2] that control physical, chemical, biological, or defense processes and devices in real-time. Increasingly, these embedded systems are part of larger *distributed* embedded systems, such as military combat or command and control systems, manufacturing plant process systems, emergency response systems, and telecommunications. A recent OMG workshop on real-time embedded and distributed object computing had commercial representatives describing distributed, real-time embedded (DRE) systems in the following domains [17]:

- Avionics

- Submarine combat control

- Satellite flight control

- Signal analysis

- · Software defined radio

- Industrial production

- Automated assembly

Middleware, such as CORBA, is being applied to these types of applications because of its ability to abstract issues of distribution, heterogeneity, and programming language from the design of systems. CORBA, specifically, has spearheaded this trend because of its development of standards supporting the needs

of DRE systems, such as RTCORBA [18], FT-CORBA [15], and Minimum CORBA [16].

More and more of these systems are networked *systems of systems*, with heterogeneous platforms and networks. Because of this, predictable real-time behavior in these DRE systems relies on the ability to do the following:

- *Manage resources end-to-end*. Real-time performance might be dominated by a single, most constrained or loaded resource, but it will rely on all the resources end-to-end, processing at each node and the network link between each node along each source-to-sink data path.

- Adapting and reconfiguring to changing conditions. In DRE systems of systems, participants might come and go, failures will happen, and mission modes will change. The system must be able to compensate for additional and changing demands, changing mission requirements and priorities, and failures.

Another characteristic of these DRE systems is that their heterogeneous resources will often have varying degrees of available control. For example, a military combat and command/control system that includes unmanned aerial vehicles (UAVs), fighter aircraft, and ground and air command and control (C2) nodes will include a variety of processing nodes, from embedded VME boards to workstations, and a variety of network links, from tactical radio links to ground IP-based network links. Tactical links currently utilize statically allocated and preconfigured time slots for dividing up the available bandwidth. Once time slots are allocated to a source-sink link, they cannot be easily changed. In contrast, dynamic reservation-based and priority-based network management is becoming available for wired, IP networks.

This motivates the need for middleware that extends the current distribution, abstraction, and limited QoS support provided in CORBA. DRE systems need *QoS adaptive middleware*, which supports the following:

- *Specification* of QoS and mission requirements, mission modes and system states, priorities, and trade offs.

- *Measurement* of system conditions, delivered QoS, and resource availability and constraints.

- *Control* of resource mechanisms, managers, and services, and of application level behavior (such as data manipulation).

- Adaptation and reconfiguration to compensate for changing system conditions, mission modes, and failures.

In this paper, we describe the Quality Objects (QuO) QoS adaptive middleware, which we have applied to the development of several DRE applications. We will first describe QuO. Then we will describe a couple of DRE applications which we have developed using QuO. Finally, we will describe the directions in which the research is proceeding.

## 2 Overview of the Adaptive QuO Middleware

Quality Objects (QuO) is a distributed object computing (DOC) framework designed to develop distributed applications that can specify (1) their QoS requirements, (2) the system elements that must be monitored and controlled to measure and provide QoS,

and (3) the behavior for controlling and providing QoS and for adapting to QoS variations that occur at run-time. By providing these features, QuO separates the role of functional application development from the role of developing the QoS behavior of the system.

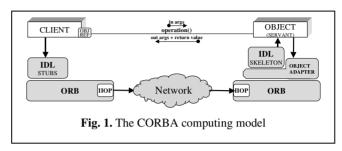

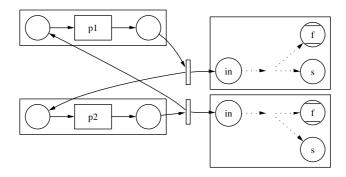

Figure 1 illustrates a client-to-object logical method call in distributed object computing as instantiated by the CORBA standard. In a traditional DOC application, a client makes a logical method call to a remote object. A local ORB proxy (i.e., a

marshals the argument data, which the local ORB then transmits across the network. The ORB on the server side receives the message call, and a remote proxy (i.e., a skeleton) then unmarshals the data and delivers it to the remote servant. Upon

method return, the process is reversed.

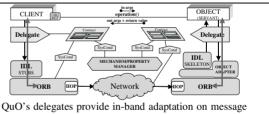

A method call in the QuO framework is a superset of a traditional DOC call, and includes the following components, illustrated in Figure 2:

- Contracts negotiate the QoS an application needs, the QoS available in the system,

- and the policies for mediating, controlling, and adapting to changes.

- Delegates act as local proxies for remote objects. Each delegate provides an interface similar to that of the remote object stub, but adds locally adaptive behavior based upon the current state of OoS in

**Fig. 2.** QuO adds components to control, measure, and adapt to QoS aspects of an application

current state of QoS in the system, as measured by the contract.

- System condition objects provide interfaces to resources, mechanisms, objects, and ORBs in the system that need to be measured and controlled by QuO contracts.

- Callback objects provide notification interfaces to clients or objects in the application.

QuO applications can use specialized QoS mechanisms, ORBs, services and managers, such as RSVP network reservation [27], the TAO real-time ORB [23], RTCORBA [18], and the AQuA dependability manager [4], respectively.

Besides the traditional application developers (who develop the client and object implementations) and mechanism developers (who develop the ORBs, property managers, and other distributed resource control infrastructure), QuO middleware

supports another development role, namely QoS developers or Qoskateers. Qoskateers are responsible for defining contracts, system condition objects, callback mechanisms, and object delegate behavior. To support the added role of Qoskateer, we have developed an open-source QuO toolkit [12, 13, 25], consisting of the following:

- A set of aspect languages, collectively called *Quality Description Languages* (QDL) for describing QoS contracts and the adaptive behavior of objects and object interactions [12, 13].

- Code generators that weave measurement, control, and adaptation code into application programs [12].

- A library of reusable system condition objects that provide interfaces to system resources, mechanisms, services, and managers; and guidelines for building custom system condition objects.

- A runtime kernel, which coordinates evaluation of contracts and monitoring of system condition objects [25].

- Object gateways for inserting measurement, control, and adaptation beneath the ORB layer [19].

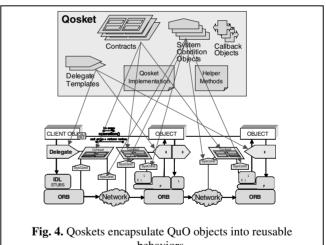

- An encapsulation model, called *Qoskets*, for localizing the code associated with a logically connected OoS adaptive behavior so that it can be referred to, and reused, as a single component, even though the behavior might be woven into various, distributed locations in the executable code [20].

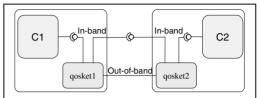

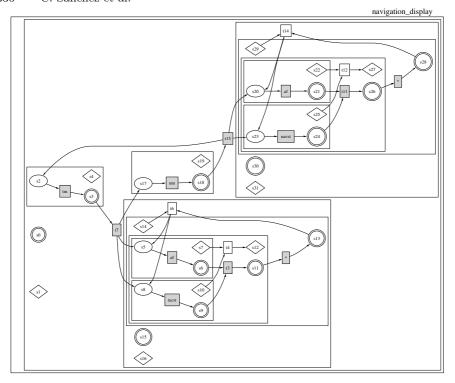

#### 2.1 In-Band and Out-of-Band Adaptation

The QuO architecture supports two means for triggering adaptation at many levels throughout the system, e.g., (property) manager-level, middleware-level, and applica-

tion-level, as illustrated in Figure 3. QuO delegates trigger in-band adaptation by making choices upon method calls and returns. A delegate intercepts method calls to sets of remote objects and adapts interactions to remote objects based on the current QoS region given by the contract. Contracts trigger out-of-band adaptation when changes in observed system condition objects cause region transitions. In this way, the contract monitors and controls the system's QoS, but operates orthogonal to and outside the in-band

(a) call and return

Out-of-band adaptation occurs when system condition objects and contracts recognize system changes

Fig. 3. QuO supports adaptation upon method call/return and in response to changes in the system

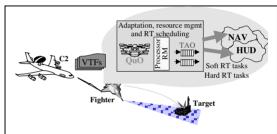

functional behavior of the system. For example, Section 3 describes QuO's use in an avionics dynamic mission replanning system. In this system, in-band QuO adaptation is used to measure the progress of and change the size of data (using tiling and quality controls) being exchanged between aircraft across a constrained network link. Meanwhile, out-of-band QuO adaptation is used to monitor the available CPU and aid in scheduling of the hard and soft real-time avionics tasks.

#### 2.2 The Qosket Encapsulation Model

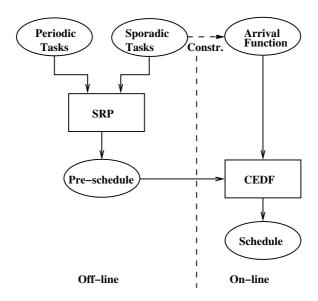

One goal of QuO is to separate the role of QoS (or systemic) programmer from that of application programmer. A complementary goal of this separation of programming roles is that systemic behaviors can be encapsulated into reusable units that are not only developed separately from the applications that use them, but that can be reused by selecting, customizing, and binding them to an application program. To support this goal, we have defined *Qoskets* as a unit of encapsulation and reuse in QuO applications. Qoskets are used to bundle in one place all of the specifications and objects for controlling systemic behavior, as illustrated in Figure 4, independent of the application in which the behavior might end up being used, and whether or not the behavior will be used in-band or out-of-band.

Qoskets encapsulate, as reusable components, the following systemic aspects:

- Adaptation policies As expressed in QuO contracts

- Measurement and control – As defined by system condition objects and callback objects

- Adaptive behaviors

Some of which are partially specified until they are specialized to a functional interface.

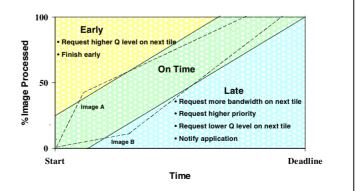

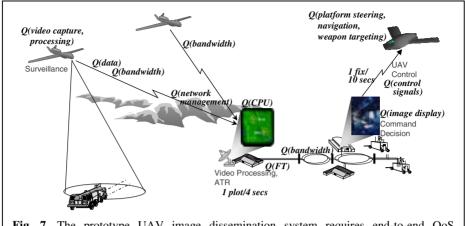

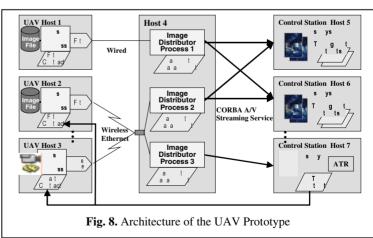

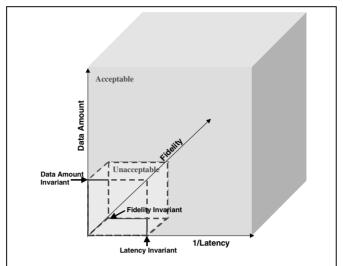

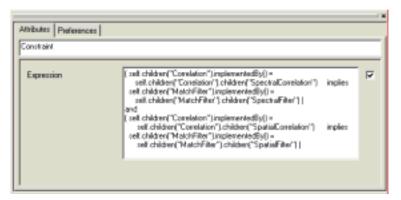

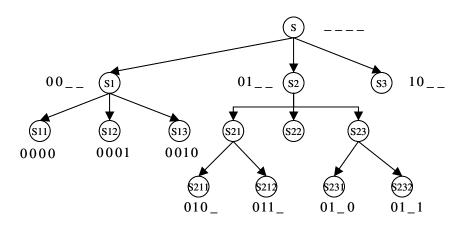

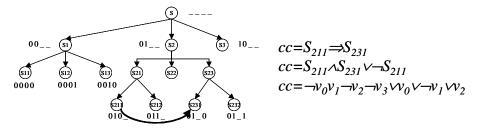

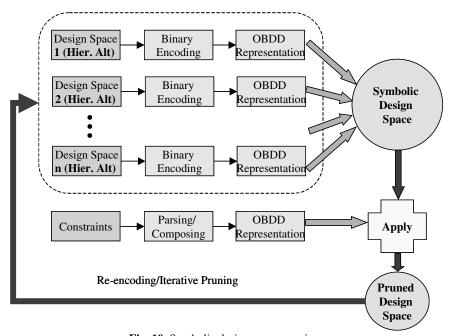

- QoS implementation